Third-party analog IP: why the market functions poorly for customers and suppliers – and how to fix it

Tim Ramsdale | CEO | Agile Analog

GSA Forum has been in virtual conversation with Tim Ramsdale, CEO of Agile Analog, a Cambridge, UK-based supplier of analog IP which implements functions in domains such as security, audio, signal conditioning, temperature sensing, data conversion, and power regulation. Agile Analog has adopted a distinctly different approach to the provision of analog IP from the conventional offering of standard IP products available from established IP vendors.

Tim’s background leading teams developing complex mixed-signal SoCs and IP for the cellular, consumer, automotive and IoT markets gives him a unique insight into the challenges of analog IP design and integration. From conversations with many customers, these challenges span the industry and are ripe for innovation to provide a step change in the level of integration we see today.

In this interview, GSA Forum asks Tim about Agile Analog’s view of the way the market works today for users of analog IP, and why he believes Agile Analog’s approach offers a better solution, both for the user and the supplier of IP.

Q: In an ideal world, how would the developers of ASICs, SoCs and other complex chips like to be able to specify and buy third-party analog IP?

A: In essence, the point of IP is to help SoC or ASIC development teams to get faster to a successful tape-out of an optimized design. To unpack that a little bit, it means reducing the development effort, it means minimizing the risk of design failure, and it means helping the designers to satisfy as many of the chip’s design specifications as possible.

So what the chip designer really wants to do is to describe a specific function or set of functions that they want to implement, buy in IP which exactly implements these functions, which is targeted to the foundry process on which the chip is going to be fabricated, which is supported by clear documentation and models which enable quick and easy integration into the rest of the chip design, and which is 100% error-free for perfect operation once the design is realized in silicon.

And unfortunately, that’s not what you get with the standard analog IP product development approach available today.

Q: Why is this? What is it about analog circuitry which makes the provision of standard IP problematic?

The problem is that the analog IP market has borrowed its business model from the digital IP world. And what works for digital IP is not well suited to analog IP.

In digital electronics, functions can be specified in a very clear-cut way: interfaces are standardized, and configurability is available at RTL level and accessible to the end user. This means that digital IP suppliers can create standard IP products which perform standard functions, with a level of configurability available to the chip integrator, confident that every user of that IP can use the same functionality. One user’s instance of 256-bit AES hash cryptography, for example, will be substantially the same as every other user’s instance. Moreover, digital IP can be synthesized to the target process by the chip integrator. This means that digital IP suppliers can create a single instance of an IP product, and it is not only portable to many processes and nodes, but can also be easily optimized for speed, performance and power through the synthesis tools.

So digital IP suppliers can make a successful business out of creating a standard IP product which they sell many times to many customers.

The analog IP market has tried to copy the same model. But it just doesn’t work in analog. That’s because of the fundamental characteristics of analog systems. In a sensor, for instance, the requirements in relation to crucial parameters such as sensitivity, accuracy, precision, linearity, stability over temperature and so on differ from application to application.

What’s more, the behavior of analog circuits varies substantially from one process and node to another, so an IP design which is perfect for one application when fabricated in one foundry on one process and node will not be perfect when fabricated on a different node, even when it’s on the same process at the same foundry. Whereas in digital, the cost of retargeting is small, thanks to digital synthesis, in analog this cost is much higher – often approaching the original design cost.

So an analog IP supplier could claim to supply for instance an ADC as a standard IP ‘product’, but in reality, every single customer wants an ADC which is unique to them.

This puts conventional analog IP suppliers in an impossible bind: either they persist in providing standard, one-size-fits-all IP products, which means that customers fail to get IP which fits their specification. So customers end up with a sub-optimal design.

Or the analog IP supplier has to become a design services supplier, reworking its IP for every design for every customer. Very often, the economics of the IP market do not support a proper design services model, so the IP supplier has to take short cuts to minimize the time and effort involved in rework.

The result is the IP user’s common experience of receiving analog IP which is not well modelled, performs poorly, and takes up precious internal development resources to make good. This is borne out by surveys we have carried out with customers: over 90% of our sample of chip designers say that they have had significant issues with analog IP that caused chip respins, and that these issues were easily found in simulations.

This of course defeats the objective of buying IP, which is to accelerate development and relieve the pressure on internal design resources.

Q: Does this also give rise to a question of trust in the quality of IP?

A: Yes, there is a growing problem of perception in the analog IP market. IP suppliers have got in the habit of describing their products as ‘silicon proven’, but this claim does not make sense if you accept that analog IP is not a standard product.

For some functions, it is possible for the IP supplier to define a fixed, unchanging set of specifications, and then to qualify a standard IP across a small number of defined foundry processes and nodes. In this case, the IP can fairly be described as ‘silicon proven’. But any deviation from this fixed design disqualifies the IP.

Today, almost all the analog IP supplied is a modified version of a standard template, rejigged to support a particular application. For all these IP instances, the designation ‘silicon proven’ is misleading.

The IP industry needs to find a different way of building trust with customers in the quality of its products. In Agile Analog’s view, this needs to be based on qualification not of a notional ‘product’ but of the process for producing the product, and then on qualification of the testing methods applied to each new instance of IP, and of the test reports supplied to the user. But the process of manual rework by which existing IP products are modified is not conducive to any rigorous or systematic method of qualification.

Q; If the model for offering ‘standard’ analog IP is broken today, what’s the alternative?

A: The starting point in the old model of supplying analog IP is the specification of the IP that the supplier has already produced. But the customer’s starting point is the customer’s specification. Conventional analog IP suppliers are in the worst of all worlds, because their ‘standard’ products do not meet customers’ needs, so they spend time and resources trying to split the difference between their existing IP and the customer’s specification. In the end, they produce IP which might be closer to what the customer wants than the original version, but is still not what the customer wanted.

And in reworking the original IP, they typically introduce bugs and defects which impair the quality of the product supplied to the customer. So no-one is satisfied – not the customer, because they do not get what they want, and not the supplier, because they spend money delivering a product which the customer does not fully value.

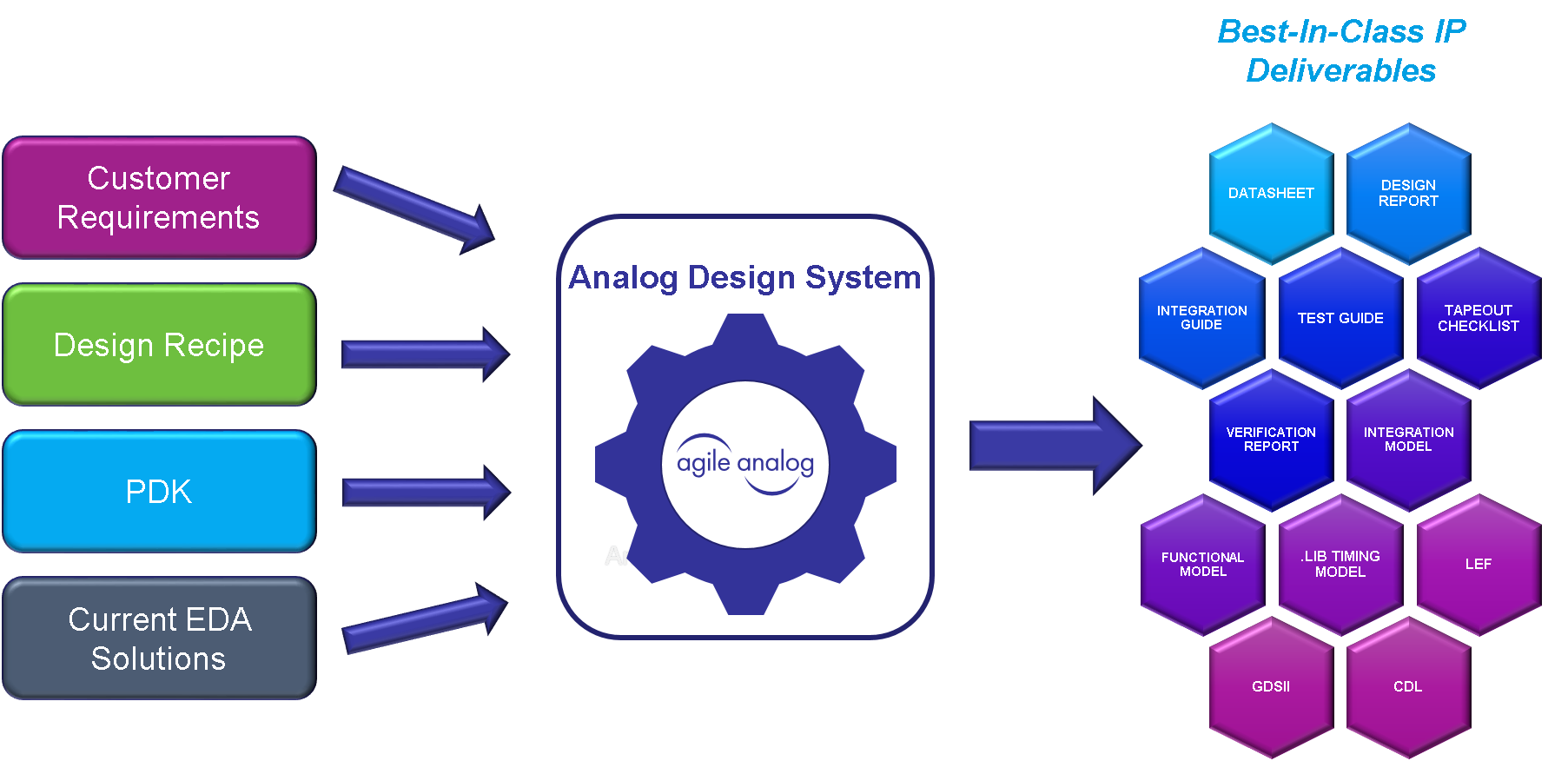

Fig. 1: the Agile Analog platform technology for generating IP unique to each customer and application

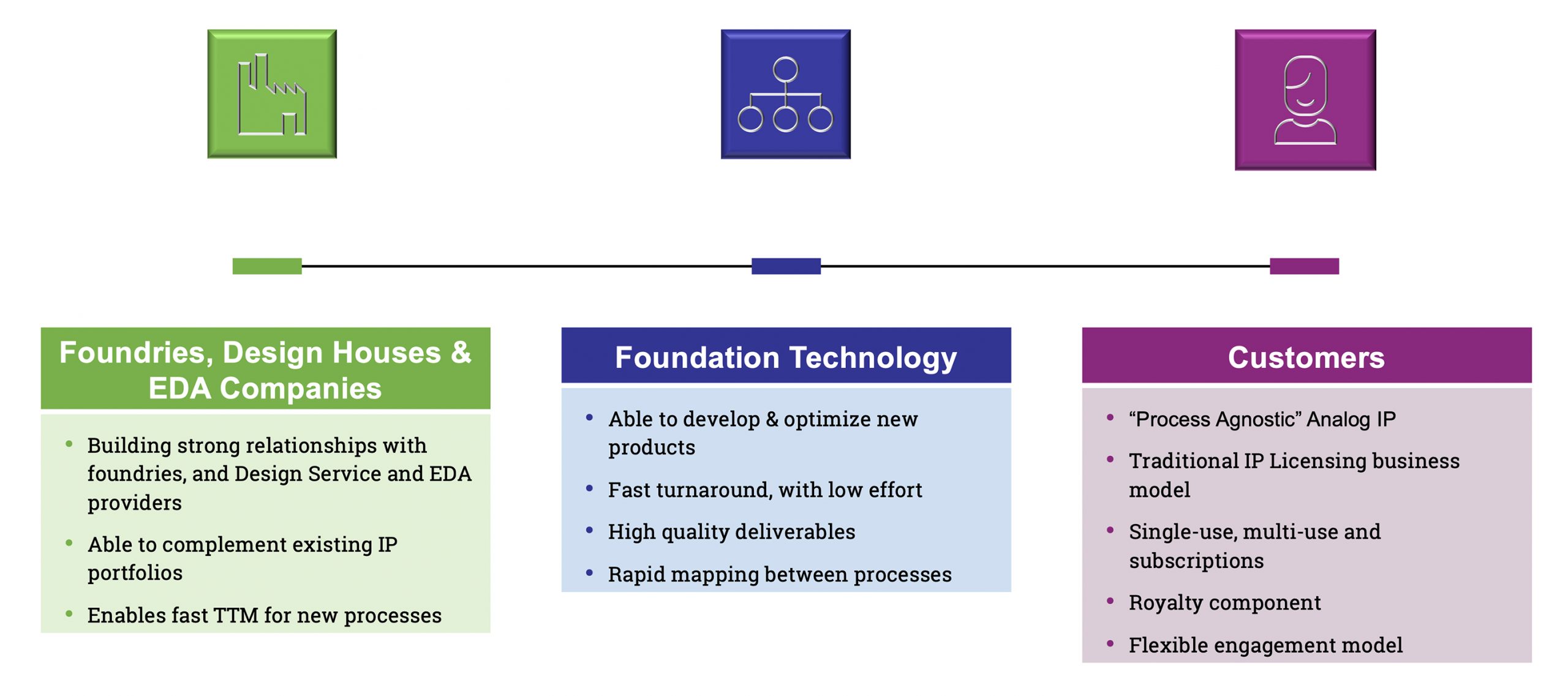

We need a new model for analog IP, one which starts with the customer’s specification. That’s why Agile Analog has developed a technology platform for generating qualified, verifiable analog IP fresh for every customer and every application (see Figure 1). Developing this platform involved the implementation of various innovations in analog design automation, artificial intelligence and simulation software. The platform today is qualified to generate IP in various functional domains such as linear power regulation, current and temperature sensing, and data conversion. The Agile Analog development roadmap will see continual expansion of the domains supported by the platform. As a result of those innovations, we are able to remodel the entire analog IP supply chain (see Figure 2).

Fig. 2: a new set of capabilities underpins Agile Analog’s remodeling of the analog IP supply chain

Now, when an ASIC or SoC designer is evaluating their analog IP options, they can come to Agile Analog, and instead of asking, ‘Which of your products best fits the specifications of my application’ – the question which they ask a conventional IP supplier – they can ask, ‘How can I optimize my design given the constraints of my chosen foundry and process?’

Within the limits of what’s physically possible in silicon, the Agile Analog platform can produce exactly the IP that the customer wants for their application. Our platform gives the customer the choice over whether to optimize for accuracy, power consumption, die area, sensitivity, speed or any other parameter, and over the way to balance the trade-offs between parameters, while meeting all the functional specifications of the design.

The Agile Analog platform can currently do all this for almost any CMOS process including FinFET processes down to 12nm. And if the customer decides to change node, process or foundry mid-design, our platform easily accommodates the change: re-optimizing and recompiling for a new process takes a matter of days, rather than the months it would take another IP supplier or a design services provider.

Q: If Agile Analog IP is newly generated for every application, how can the customer gain quality assurance for it?

A: It’s about proving the process rather than the product. We know, because we have taped out multiple sample designs, that our entire IP generation process is qualified, and to as high a quality standard as any applied in the semiconductor IP industry.

The customer can evaluate and test the quality through the extensive deliverables provided during the IP generation process. At every stage in the process, from functional description to verification to integration to testing, the customer receives detailed datasheets, simulations and test reports which fully document the performance and characteristics of the IP. The whole process is automated and repeatable: after the first output is verified, every subsequent output of the process is guaranteed to be verifiable.

Q: What should ASIC or SoC designers who are new to the process expect?

A: Buying Agile Analog IP is a radically different process from customers’ previous experiences of buying analog IP. Agile Analog starts the process by asking the customer what they want. Chip designers who have bought analog IP the traditional way are used to settling for ‘good enough’: with Agile Analog, you get analog IP the way you want it.

We ask customers to be bold, and to let go of their assumptions about the limited choices available to them. We want them to think about what they really want, not to limit themselves to what they think they can get.

This means that the specification process is much more interactive than in a standard IP engagement. We encourage a to-and-fro with our customers. We invite them to explore the full range of optimizations which our platform technology supports, so that, at the end of the process, the IP that they embed in their chip is as close as possible to their ideal.

That’s what our platform technology is all about – providing to the customer IP which is easy to integrate into their chip design and fabrication process, which is optimized for their design and process, and which frees the design team to focus on the unique, added-value functionality for which there is no third-party IP.

________________________________________________________________________________________________

Agile Analog’s press representative:

Rhianna Ogle

TKO Marketing Consultants

E: rhianna@tko.co.uk

T: +44 7866 997774