# **RISC-V**, the next generation architecture for Al

تاريد المراد ا

huminit

October 2024 GSA Executive Conference

### **Ventana RISC-V AI/HPC Engagements**

**Common Themes Have Emerged In Discussions With Hyperscalers, Sovereigns, OEMS, And End Customers**

### Compute architectures are changing forever...

0 0 111 0 0 111 0 0 111

... there will be pervasive use of AI across all applications

### **AI WILL BE Pervasive Across All Applications and Markets**

- Software Development: Developer productivity boosted significantly through automatic code writing, refactoring, and documentation,

- **Content Creation:** Automation of content creation enhancing marketing and sales productivity

- **Customer Service:** Virtual assistants to automate tasks and personalize responses

Data Center

- silicon will be necessary to support Al-driven operations and enhance efficiency

- Power and Coiling: Al workload demands require advanced power systems and liquid cooling

- Sustainability: Energy costs, efficiency and availability drive architecture and locationre of data centers

- ADAS and Driver Assist Systems: AI powering the next jump autonomous driving systems

- Predictive Maintenance: anticipates vehicle issues before they occur, reducing downtime and maintenance costs, while optimizing fuel efficiency and performance through real-time data

- **Laptops:** Al processing capability now a requirement for next generation PCs

- **Mobile:** Al longstanding capability for features such as photo enhancement

- Industrial Manufacturing: Efficient, scalable, low latency Al required for next generation robotics manufacturing capabilities

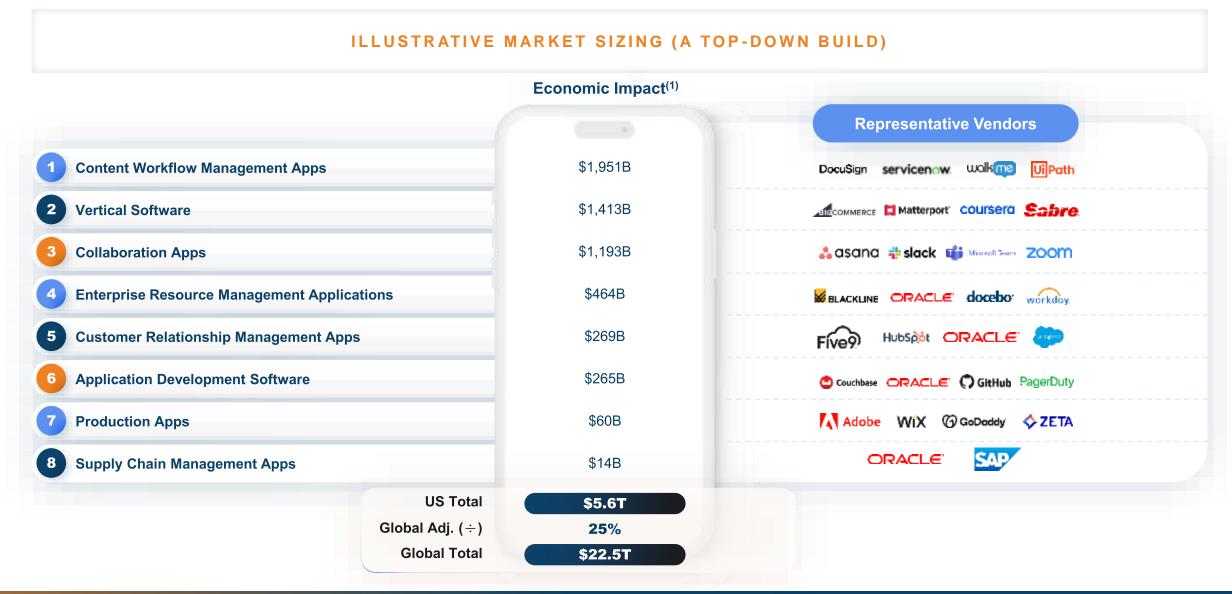

### **\$22.5T Global Economic Impact Estimated For Generative Al**

Source: Equity Research.

Represents the cumulative wages that can be impacted by GenAI. Calculated by estimating % of employment impacted in 3 years (the estimated number of years for household adoption) by the average wage by occupation.

$\sim$  ventana  $\,$

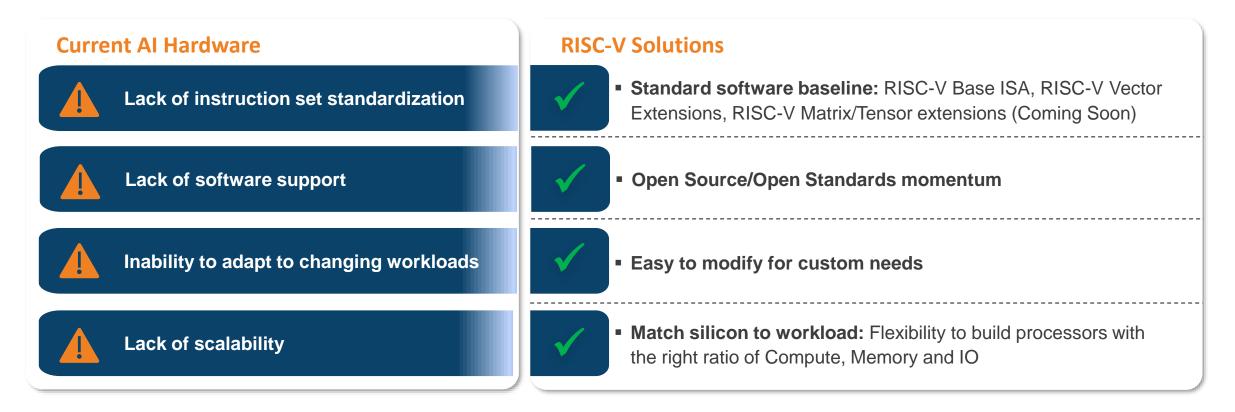

# **Pain Points With Current AI Acceleration Solutions**

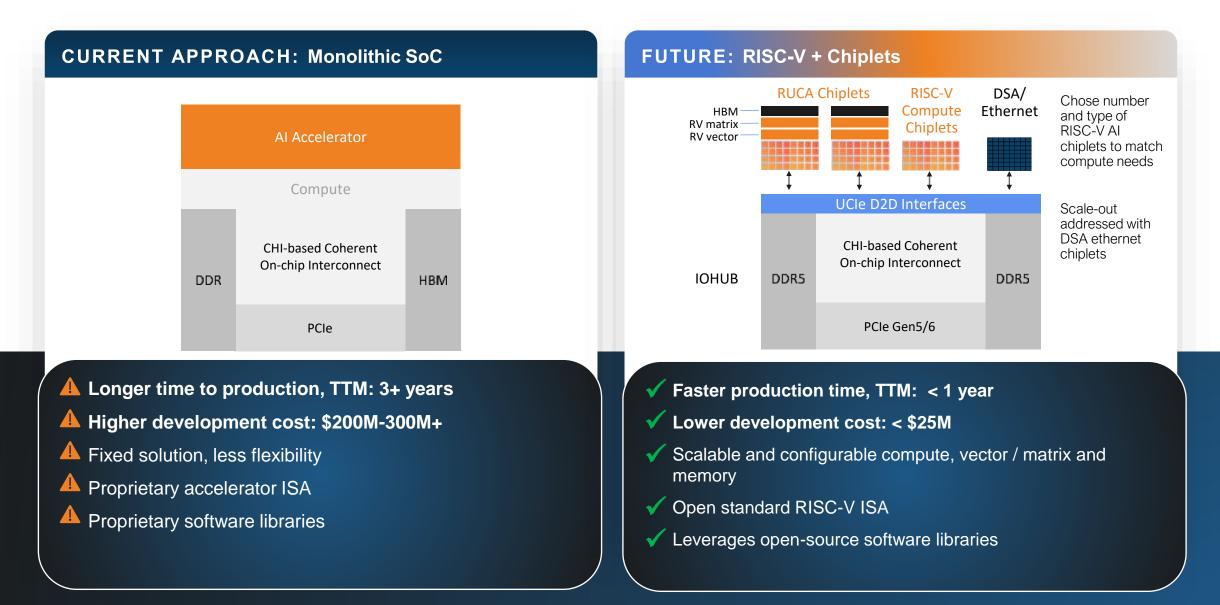

### Current solutions take a "one-size-fits-all" approach to hardware development

### Overoptimization For Yesterday's Architectures

- AI models evolve: AlexNet $\rightarrow$ ResNet $\rightarrow$ Transformer $\rightarrow$ LLMs $\rightarrow$ ?

- Many ResNet accelerators underperform on Transformer workloads

### Inability to Right-Size for Workloads

- Flexibility to adjust Compute, Memory, and IO to specific applications

- Tight CPU-AI integration required

### • Need to Keep Up with rate of AI Innovation

- Current solutions lock users into specific vendors

- Customization for changing AI architectures is critical

- Open Hardware and Software Stacks required

### **RISC-V Solutions are Key to Overcoming AI Chip Challenges**

### Varied ISAs, Fragmented SDKs, and Limited Software Are One of the Biggest Limitations of AI Hardware Usefulness

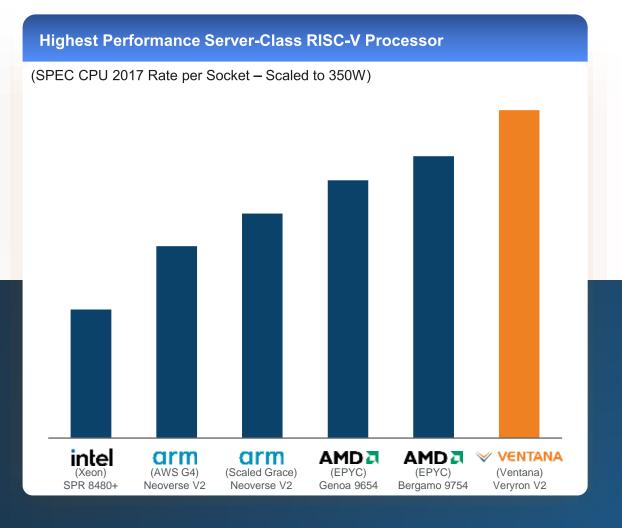

### VENTANA has the Highest Performance RISC-V CPU in the World

#### VENTANA'S NEW VEYRON V2 IS THE HIGHEST PERFORMANCE RISC-V PROCESSOR AVAILABLE TODAY AND IS OFFERED IN THE FORM OF CHIPLETS AND IP

- Veyron V2 showcases up to 40% improvement in performance

- Improved RISE ecosystem support enables V2 to quickly deploy open, scalable, and versatile solutions

- Chiplet-based solutions improve unit economics, accelerating time to market by up to two years and reducing development costs by up to 75%

- Domain specific accelerator designed to enhance workload efficiency

# Up to

**192 Cores** Multi-cluster scalability

**3.6GHz**

128MB Shares L3 cache per cluster

4nm

Process

technology

32 Cores Per cluster

**512b**

Vector unit

💛 VENTANA

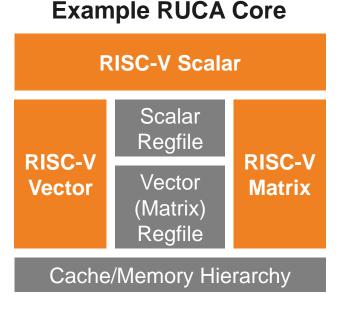

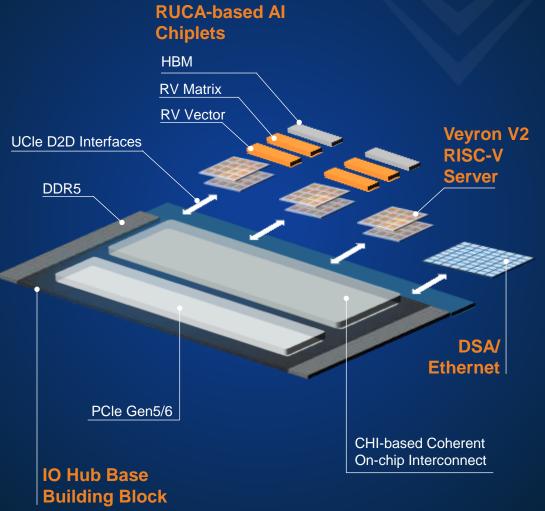

### The Solution: RUCA RISC-V Unified Compute Architecture

### • RUCA Cores Use Standard RISC-V Scalar-Vector-Matrix Operations

- Open Standard Software Target

- Unified Instruction Set

- Tightly Coupled Shared Register Files and Cache Hierarchy

- RUCA Cores Have Ability to Add Custom Extensions to Enhance the RISC-V Base ISA

### RUCA Architecture Advantage

- RUCA Cores contain the entire Host(Scalar) Accelerator profile: Avoids Expensive Data Transfers and Compute Hand-Offs

- Typical GPU/AI Offload Accelerators Require Extensive Shuffling of Data Across Board/Fabric

Incubate AI Innovation with RISC-V Custom Extensions, Drive to RVI Ratified as Value Proven

### **Chiplets Deliver Efficient and Scalable Al**

$\checkmark$  ventana

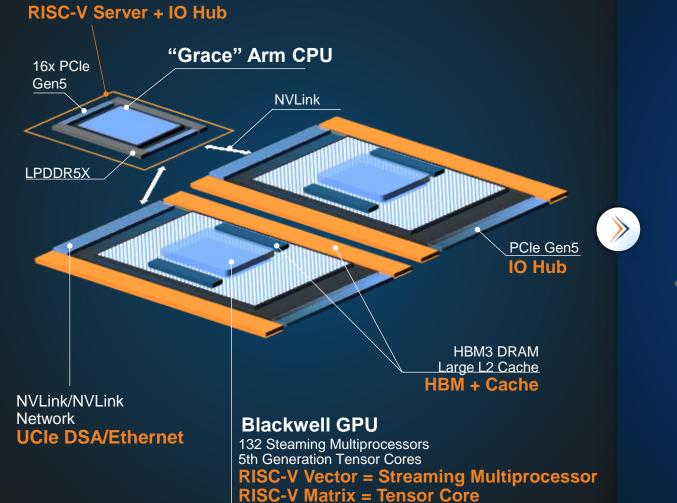

### **Nvidia Grace Blackwell Deconstructed Into RUCA**

### **RISC-V** Equivalents to Nvidia Grace Blackwell

### **AI Compute Using RISC-V**

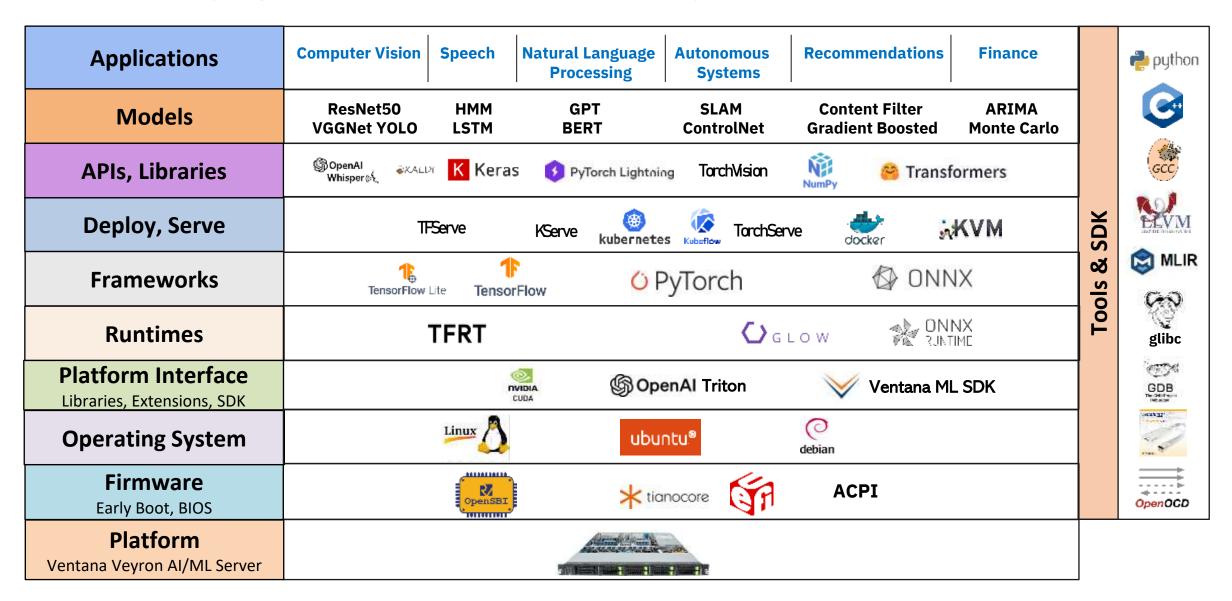

# **RISC-V AI/ML Software Ecosystem**

Work has already begun to enable the RISC-V software ecosystem

# **The Complete RISC-V Veyron Platform**

#### Tensor accelerators and custom instructions are not enough

Al will be pervasive across all tiers of computing

- A common architecture and software base is required for mass deployment

- The RISC-V Unified Compute Architecture enables the efficient development of AI software and libraries

- Achieving this vision requires a complete platform

- Ventana, through its platform, will partner to make RISC-V a driving force in the advancement of AI

# Thank You !

### Ventana Founding Team Overview

**Balaji Baktha** FOUNDER AND CEO

**Pioneer in Data Center semiconductors:**

33+ years experience

- World's first 64-bit ARM with Veloce (Acquired by AppliedMicro)

- Led Marvell BU delivering Data Center class Networking, Communications, Compute, Storage and Wireless infrastructure products

- · World's first iSCSI with Platys, (Acquired by PMC-Sierra (Adaptec))

**Greg Favor** CO-FOUNDER AND CHIEF ARCHITECT

One of the world's leading **CPU architects:**

- 35+ years experience

- Architected K6 processor at startup NexGen, acquired by AMD

- Chief Architect at Siara Systems, acquired by RedBack

- Architected first successful 64-bit ARM CPU

THE SAME TEAM THAT DESIGNED AND SHIPPED THE WORLD'S 1ST 64-BIT ARM SERVER EXTENSIVE EXPERIENCE FROM PIONEERING PROCESSOR COMPANIES